Research

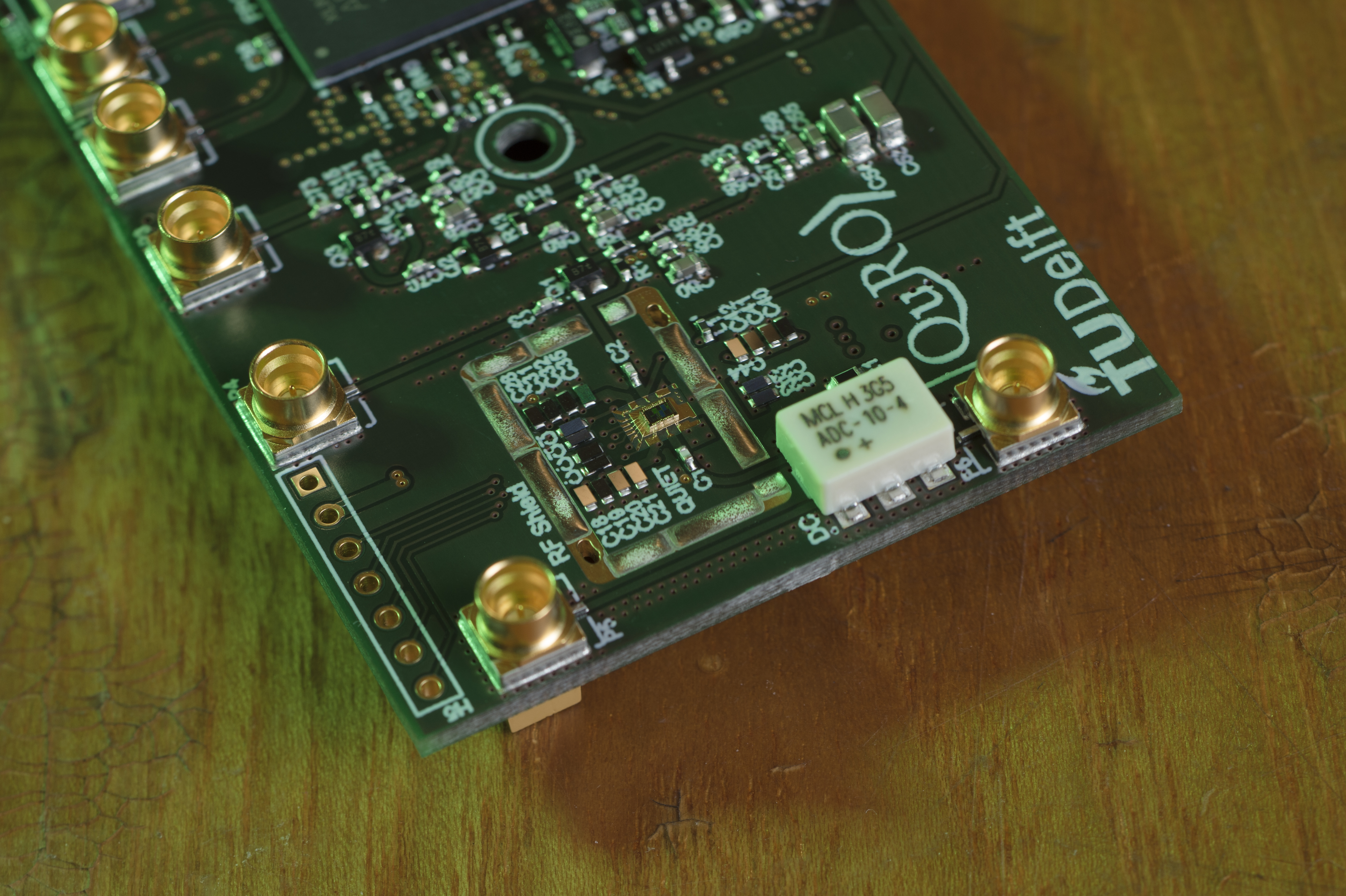

Our research is focussed on developing the electronic interface for quantum devices in quantum computers and quantum sensors. We design, fabricate and test integrated circuits in commercial microelectronic technology, e.g., 40-nm CMOS, 22-nm CMOS and SiGe BiCMOS, with the aim to operate them at cryogenic temperatures (4 K and below) very close to the cryogenic quantum devices.

The group is led by Dr. Sebastiano, expert in analog and mixed-signal electronics, and Dr. Babaie, expert in RF electronics, and targets the development of all RF, analog, mixed-signal and digital circuits required to control and readout quantum devices in a quantum computer or in a quantum-sensing system (see below).

The research is funded both by industry, such as via the large collaborations we have with Intel and Fujitsu, and via public funding through NWO and EU grants. We are also members of QuTech and closely collaborate with the other research groups in the QCE department , in QuTech and in the Applied Physics faculty working on quantum algorithms, computer architectures and quantum devices.

In addition to our conference and journal papers, we are heavily involved in the Technical Program Committee of several world-leading conferences such as ISSCC, RFIC, IMS, ESSCIRC, and organize and contribute to workshops, tutorial and invited talks at international venue, such as IEDM, IEEE Quantum Week, and CICC.

Openings for PhDs and Postdocs

Please contact Dr. Sebastiano or Dr. Babaie directly if you wish to work with us. Several opportunities are available!

Further reading and resources

• Our research on a cryo-CMOS chip driving a spin qubit published in Nature

• Dreaming of the quantum computer – an interview with Fabio Sebastiano

• IEEE SSCS webinar on cryo-CMOS electronics

• Website of the TU Delft-Fujitsu collaboration

Overview of Research Themes

Cryo-CMOS

Quantum computers hold the promise to ignite the next technological revolution as the classical computer did for last century’s digital revolution, by efficiently solving problems that are intractable by today’s computers, such as large number factorization and simulation of quantum systems. Solid-state quantum processors must be typically cooled at cryogenic temperatures (<<1 K). In addition, a classical electronic controller is required to initialize, control and read out the quantum bits (qubits) at the core of the quantum processor. Currently, the most advanced quantum processors are equipped with less than 100 qubits, thus making it possible to connect a limited number of cables from the cryogenic refrigerator to a room-temperature electronic controller. However, quantum algorithms for practical applications require up to thousands or millions of qubits and of related connections, thus making the wiring to a room-temperature controller unpractical.

As an alternative, we propose a scalable CMOS electronic controller operating at cryogenic temperatures as close as possible to the quantum processor, in order to simplify the interconnect and to provide a solution scalable up to thousands of qubits. Although building a cryogenic CMOS controller is feasible, there are several challenges to be addressed. First, there is not yet a standard cryogenic model that can be embedded in commercial design tools and valid in the GHz-frequency range and/or for nanometer CMOS technologies. Missing reliable models strongly restrain the use of advanced techniques and the complexity of any circuit design. Second, specific cryogenic design techniques must be developed to deal with non-idealities of CMOS devices at cryogenic temperatures. Third, the cooling power of state-of-the-art refrigerators is limited to a few Watts at 4 K and well below 1 W at sub-K temperatures. This poses a strict specification on the power consumption of the electronics, thus forcing the average power consumption of the cryogenic controller below a few milliwatt per qubit.

In addition to quantum computing, advances in cryogenic electronics will also be employed in many other low temperature applications. Examples include cryogenic sensors and/or electronic read-outs for high-energy physics experiments, detectors for radio-astronomy, cryogenic probes for nuclear magnetic resonance (NMR) used in chemical and medical spectroscopy, and instrumentation for spacecraft and orbiting observatories.

Cryo-CMOS modelling

The aim is to characterize devices from several CMOS technologies over a wide range of cryogenic temperatures (30 mK – 77 K) and develop models suitable for analog and digital circuit design over such range. Currently, we have already fabricated and characterized test structures in 0.16-μm CMOS and 40-nm CMOS

and, in collaboration with Prof. A. Valdimirescu (UC Berkeley/isep), we have been able to build a device model that is compatible with standard integrated-circuit design tools and that has been used for successfully designing complex analog circuits.

Controllers for quantum processors

Designing a quantum computer will require co-optimizing the classical controller and the quantum processor. We are engineering such system and deriving the specifications for the electronics, by both analyzing and simulating the physics of the quantum devices and by experimenting on existing quantum processors. Today, we are already able to derive a complete set of specifications and trade-offs for the electronic controller for single-electron spin qubits.

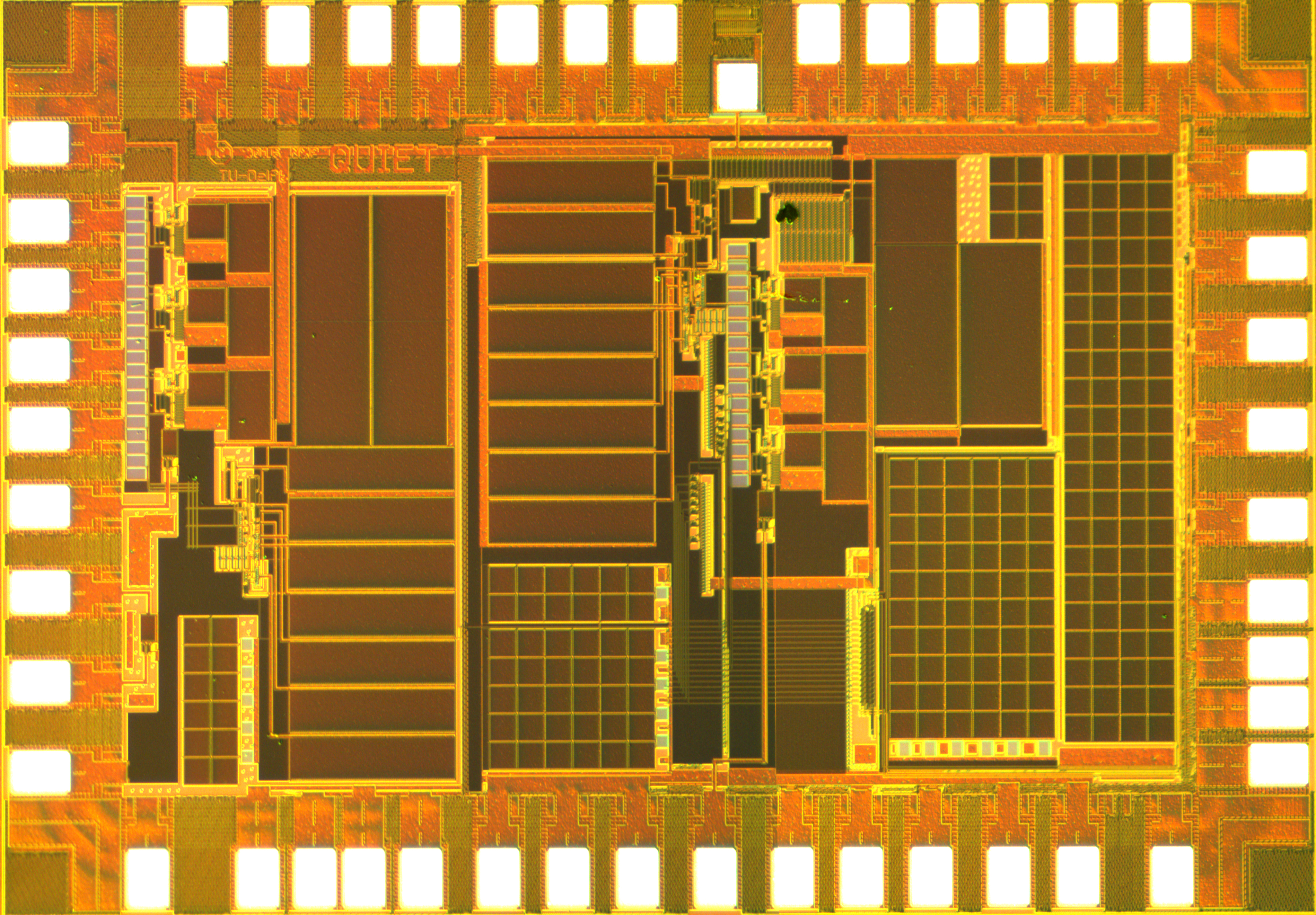

Cryo-CMOS circuits and systems

Capitalizing on our broad research experience on RF/analog/mixed-signal CMOS electronics at room temperature, the group is developing cryogenic circuit blocks to be integrated in the controller, including signal multiplexers and demultiplexers, amplifiers, analog-to-digital and digital-to-analog converters. We will explore the trade-offs between operating temperature, available refrigeration power and functionality, that could result in some components working at 4 K or higher temperatures and others at mK temperatures, possibly on the same die with the qubits. We have already been able to demonstrate the functionality of a low-noise amplifier in a standard CMOS technology operating at 4 K.

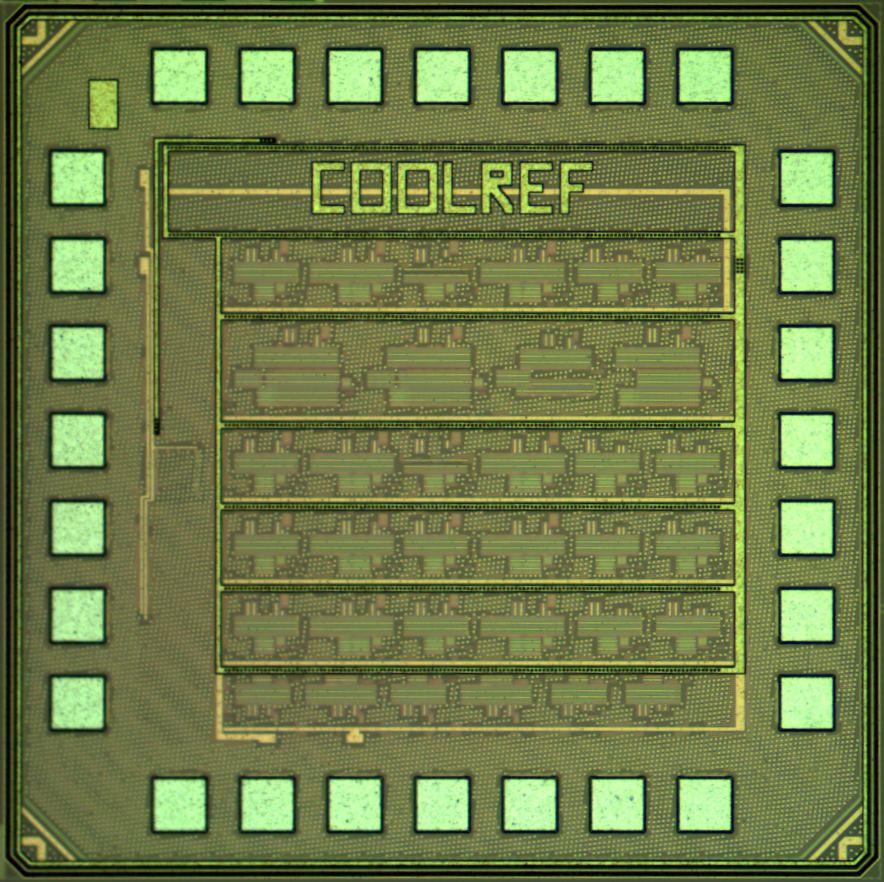

Cryogenic temperature sensors & references

The objective is the development of supporting electronics for the controller, such as on-chip temperature sensors, references (current, voltage, frequency) and supply regulators, which are required for proper operation of any circuit block at cryogenic temperature. Having characterized the cryogenic behavior of standard CMOS devices employed in integrated voltage references and temperature sensors, we are currently investigating how to use those devices for references and sensors operating over a wide temperature range from 300 K down to 4 K and below.

Cryogenic digital circuits

Building a computing device such as a quantum computer requires a large amount of classical logic, for instance to provide hardware support for the quantum microarchitecture and to process the digital signals from and to the data convertrs directly connected to the quantum processor. Our objective is to exploit the specific advanatges of cryo-CMOS devices, such as the extreme low leakage and the high-subthreshold slope, to design cryogenic logic with superior performance.